# SIRIUS FAST BEAM ORBIT INTERLOCK SYSTEM

## L.S. Perissinotto, M.M. Donatti, F.H. Cardoso, D.O. Tavares, J.L.N. Brito, A.C.S. Oliveira, E.N. Rolim, A.F. Giachero, G.R. Cruz, F.H. de Sá, T.M. da Rocha, G.G. Saretti, LNLS, Campinas, Brazil L. M. Russo, LBNL, Berkeley, CA 94720, USA

## Introduction

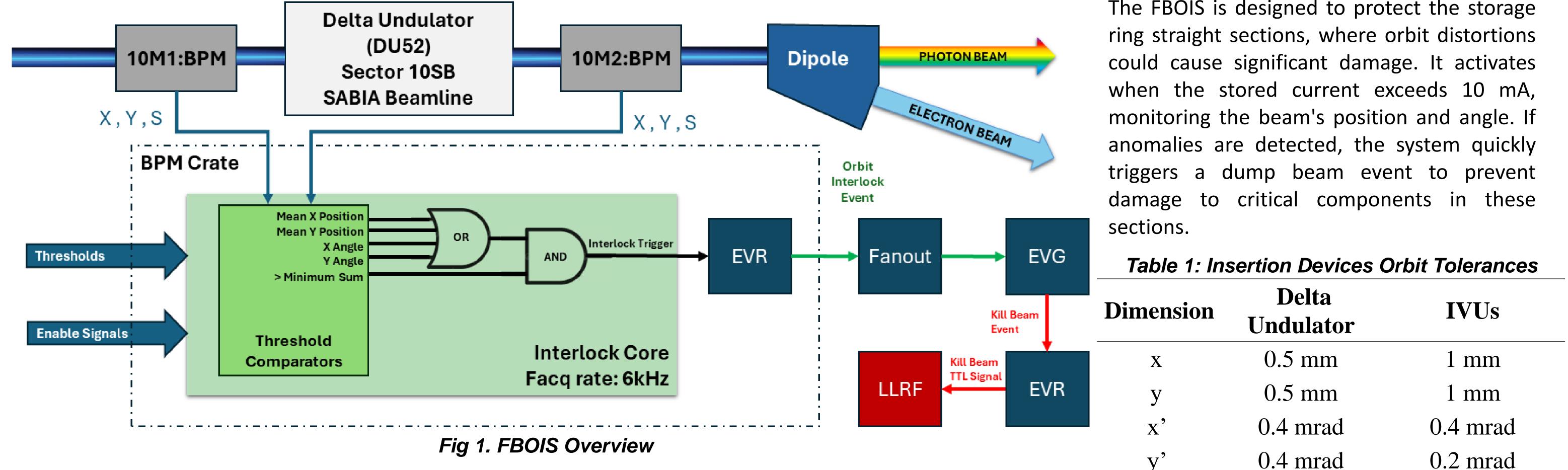

Particle accelerators use fast interlock systems to prevent damage from harmful beam position changes. In synchrotrons, insertion devices (IDs) are critical, as misaligned beams can damage storage ring (SR) and front-end (FE) components. SIRIUS, a 4<sup>th</sup> generation synchrotron facility with three high-brightness light sources, implemented a Fast Beam Orbit Interlock System (FBOIS) to protect its devices, including a Delta undulator [1] and new in-vacuum undulators (IVUs).

The FBOIS is designed to protect the storage

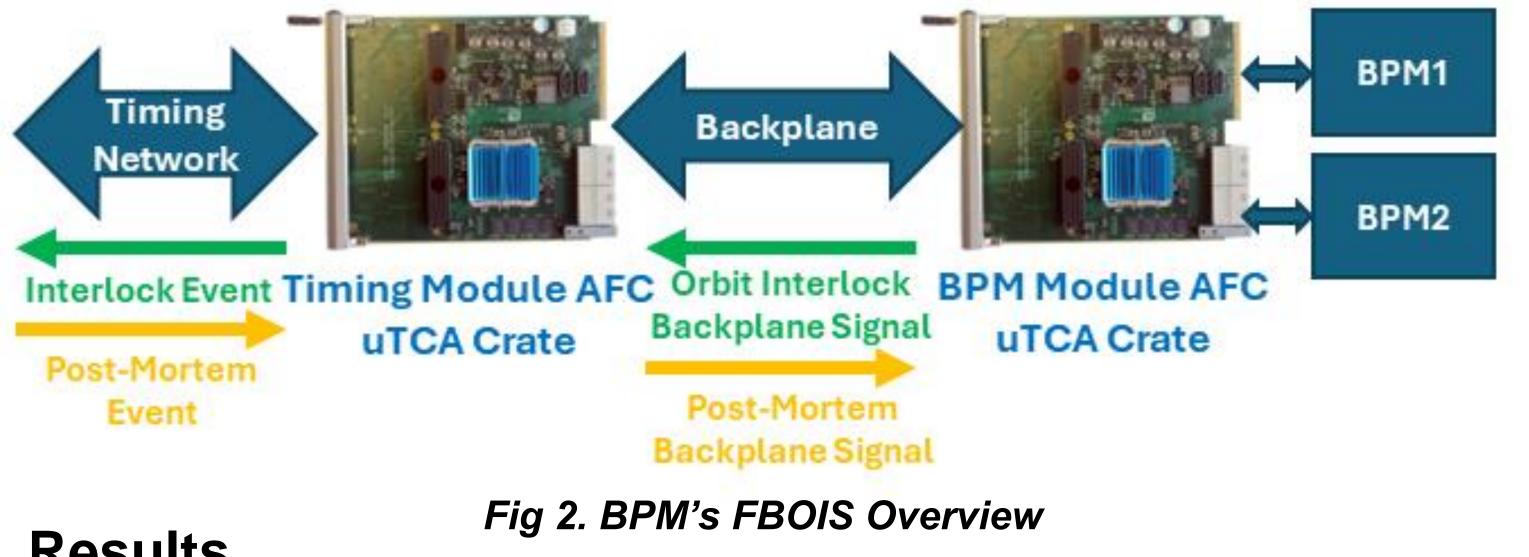

#### **BPM's Overview**

The BPM digital board [2] and the timing receiver [3], developed with FPGAbased MicroTCA.4 AMC cards, support the Fast Beam Orbit Interlock System (FBOIS) without needing extra hardware. The BPM calculates beam position and angle at a 6 kHz sample rate. If the beam exceeds configured thresholds, the system triggers an interlock event, initiating a post-mortem data acquisition across all BPMs. Data is stored before and after the trigger for analysis.

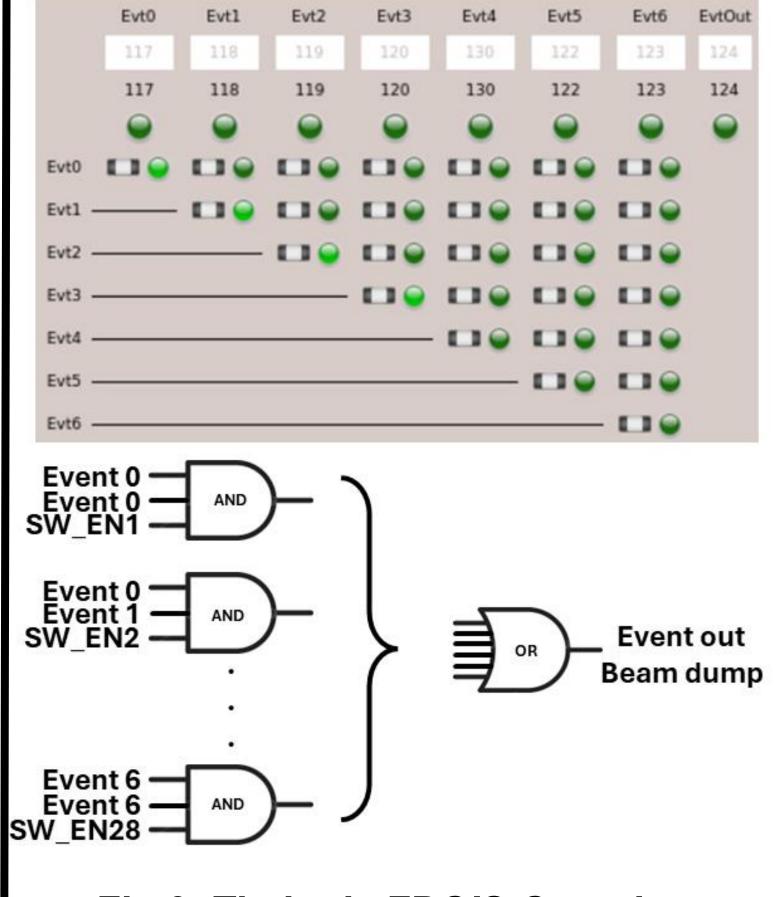

#### **Timing Overview**

SIRIUS uses a uses the timing system developed by SINAP in a star topology with a full-duplex link implementation [4], enabling event propagation both downstream and upstream. The system is composed by modified SINAP devices MicroTCA.4 in-house timing and modules, which communicate via a

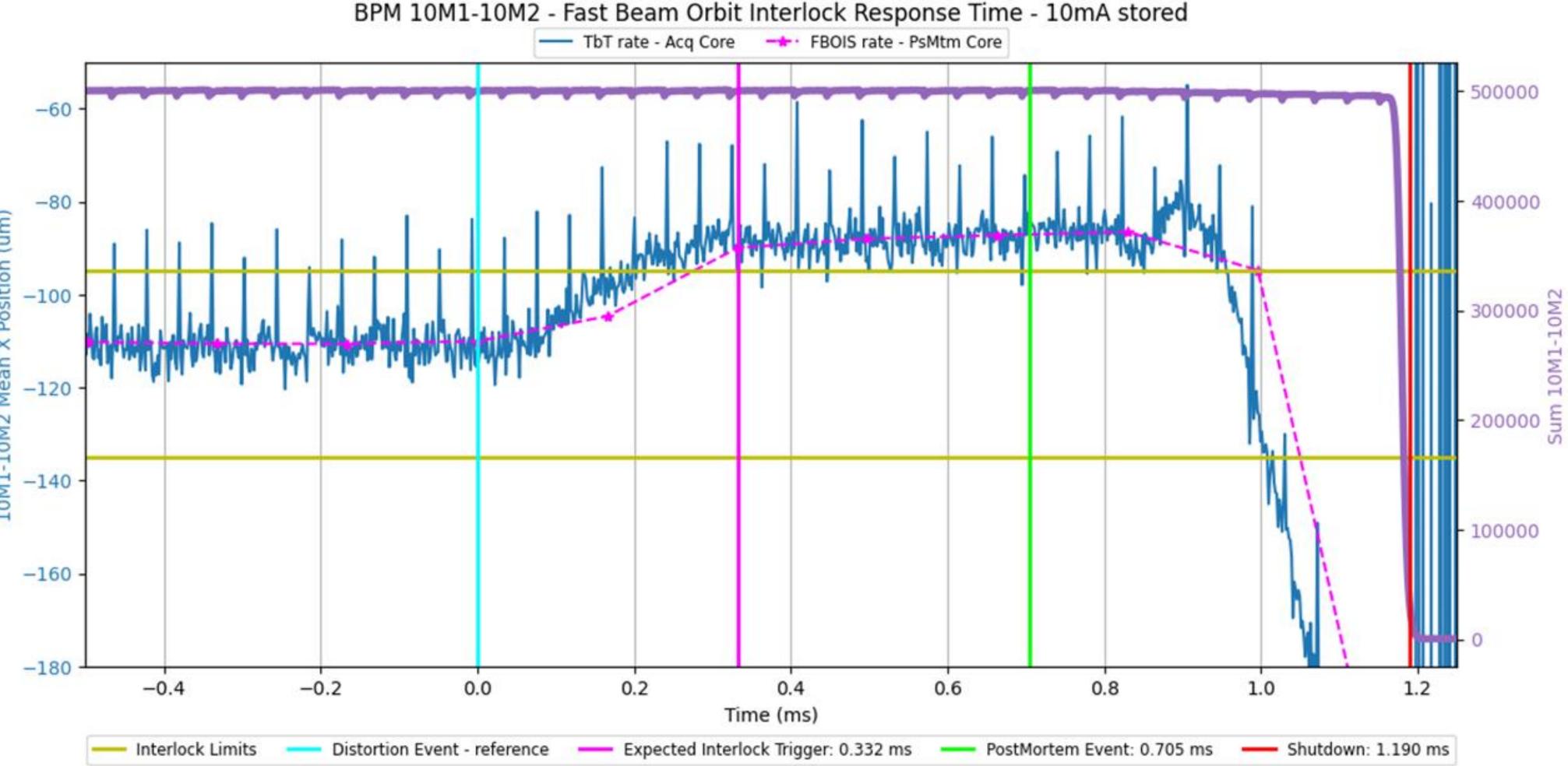

## **Results**

The Fast Beam Orbit Interlock System (FBOIS) at SIRIUS was tested during machine shifts to ensure reliability. The tests involved injecting current into the storage ring, setting a position threshold for interlocking, and creating a position distortion using a horizontal corrector. This distortion triggered an upstream interlock event, which led to the Event Generator (EVG) sending a "kill beam" signal to disable the Low-Level RF (LLRF) and trigger postmortem data acquisition in all BPMs. During a test with 10 mA current, a worst-case delay of 1.190 ms was observed between the distortion event and beam shutdown. Additionally, a high-level application monitors FBOIS-enabled devices and can disarm the LLRF if any link becomes unavailable.

Fig 3. Timing's FBOIS Overview

backplane bus with other components like BPM modules. A key feature is the Event Generator's (EVG) interlock map, which triggers downstream actions, such as a "kill beam" event, based on upstream signals. This interlock map also manages events logging to build beam loss incidents timeline.

IBIC2024

**Beam Loss Monitors and**

BRAZILIAN GOVERNMENT

UNITING AND REBUILDING

**Machine Protection**

## Acknowledgments

The authors would like to gratefully acknowledge the funding by the Brazilian Ministry of Science, Technology and Innovation (MCTI), and the contributions of the LNLS teams enrolled in Sirius project.

Fig 4. Distortion and Fast Beam Interlock response curve

#### References

[1] L. N. P. Vilela, R. Basílio, J. F. Citadini, J. R. F. Jr e F. Rodrigues, "ADVANCES IN THE SIRIUS DELTA-TYPE UNDULATOR PROJECT". IPAC2018. [2] D. O. Tavares et al. "DEVELOPMENT OF AN OPEN-SOURCE HARDWARE PLATFORM FOR SIRIUS BPM AND ORBIT FEEDBACK". ICALEPCS2013. MINISTRY OF [3] J. L. N. Brito et al. "A MicroTCA.4 TIMING RECEIVER FOR THE SIRIUS TIMING SYSTEM". IBIC2018. SCIENCE TECHNOLOGY AND INNOVATION [4] J. L. N. Brito et al, "STATUS DEVELOPMENT OF SIRIUS TIMING SYSTEM". ICALEPCS2015.