# Design and performance test of 8 channel 125 MS/s digitizer with 16-bit resolution for BPM and LLRF application

Qiutong Pan, Tao Xue, Haoyan Yang, Bo Liang, Lin Jiang, Tsinghua University, Beijing, China

In modern accelerator applications, stringent require-ments are placed on the noise performance of digital converters. The noise from the digital converter will become part of the field noise seen by the beam, thus necessitating a low-noise, low-crosstalk digitizer. In response to this demand, this paper presents the design of a digital converter circuit board with 8 analog-to-digital converter (ADC) channels which has been subjected to testing. The test results indicate that the circuit board possesses low noise characteristics, rendering it suitable for reading accelerator signals.

## Hardware Design

Motivation

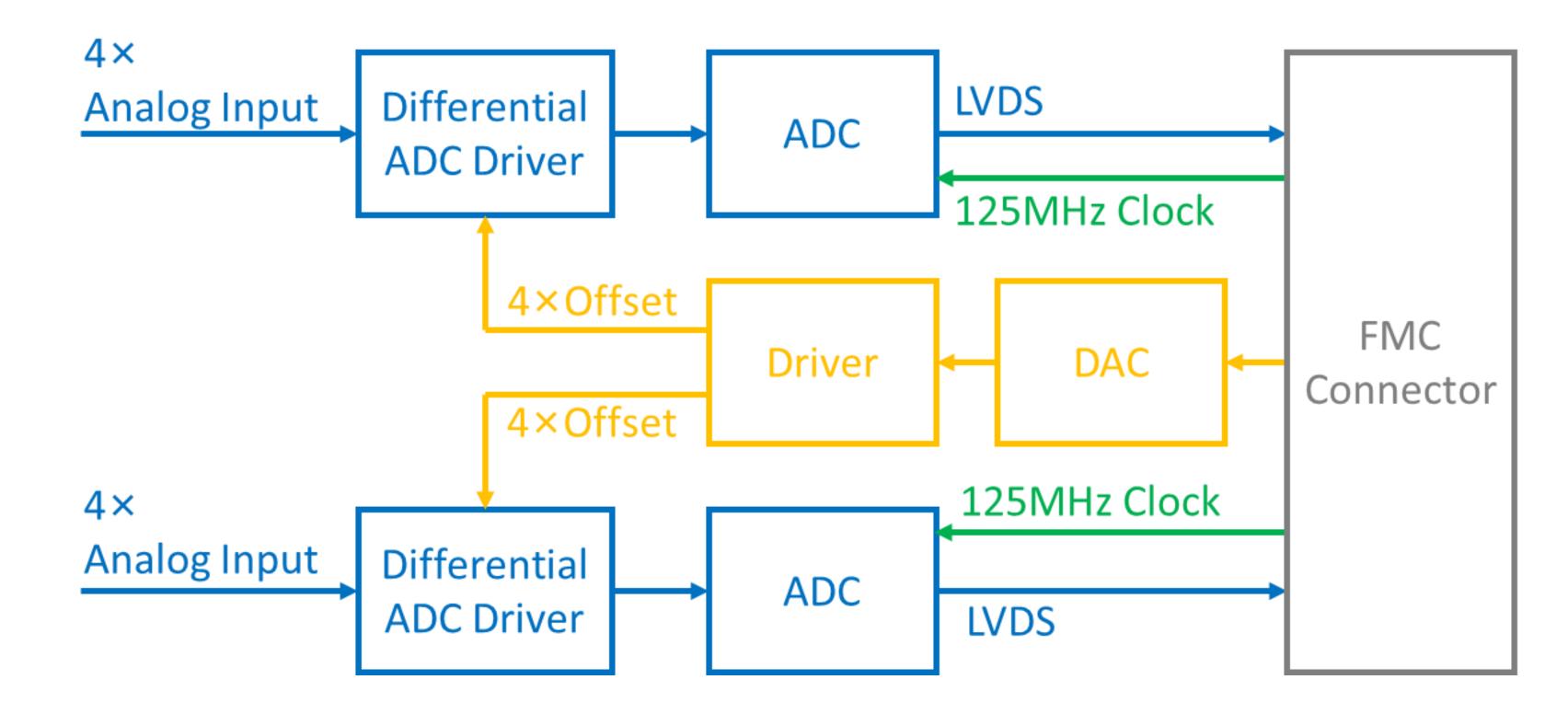

Figure 1 is the design block diagram of the mezzanine card. The circuit board has 8 SSMC RF connectors, providing 8 analog signal inputs for the ADC. The single-ended analog signal is converted into a differential signal after passing through the fully differential ADC driver. In addition, in order to facilitate the adjustment of the DC voltage component at the ADC input, the DAC output set voltage value is also required to be connected to the reverse input of the fully differential amplifier. The input clock of the ADC is 125MHz, which is provided by the FMC connector. After the ADC collects and converts the analog signal, it is transmitted to the FMC connector in the form of an LVDS signal, and then provided to the FPGA.

Figure.1. AD9653 Readout Logic Block Diagram

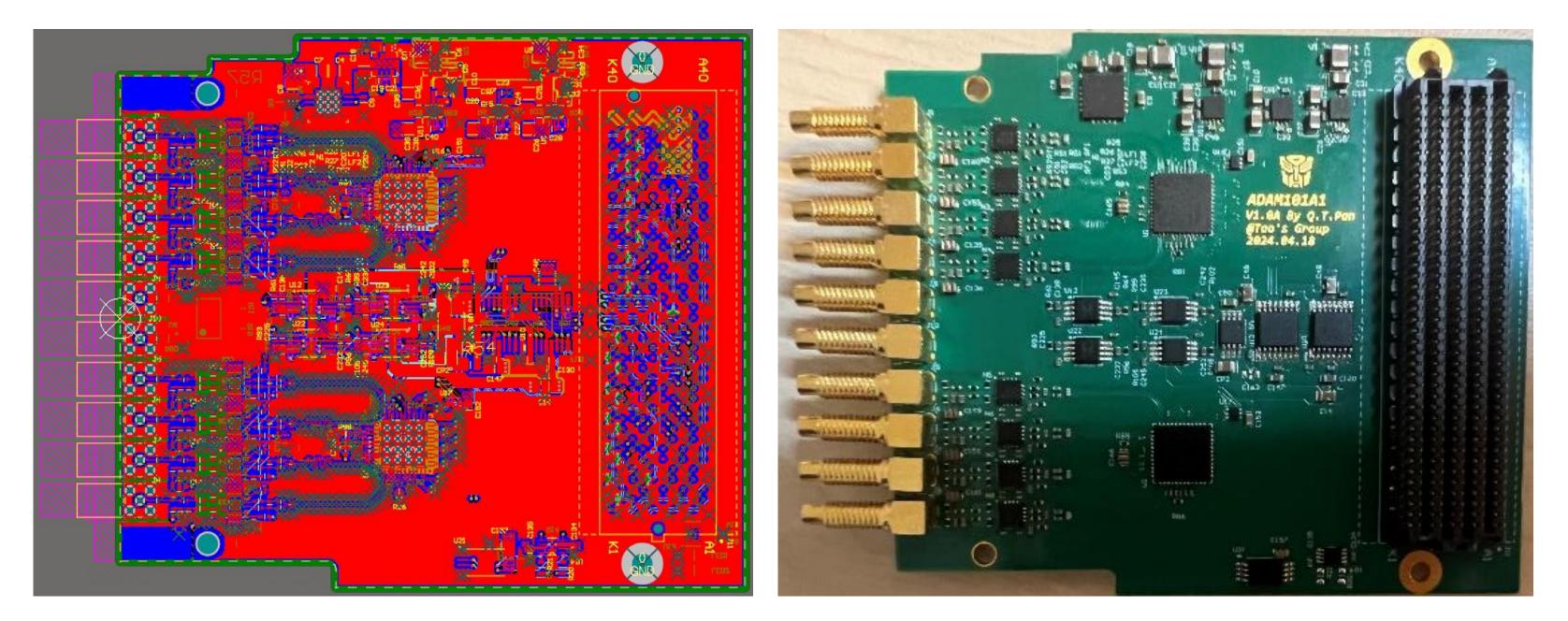

Figure 2 is the design PCB drawing of the mezzanine card, and the actual picture of the PCB after welding. The PCB has a total of 8 layers, which can be divided into ground, power and signal layers. When de-signing, attention should be paid to impedance matching and data line length processing. In addition, during the design process, through a brief evaluation of noise, a low-noise power supply solution was selected to achieve better performance.

The ADC is ADI's AD9653, which is a 4-channel, 16-bit,

125MSPS ADC with a conversion rate of up to 125MSPS, excellent dynamic performance and low pow-er consumption. The DAC is ADI's AD5686, which is a lowpower, four-channel, 16-bit buffered voltage output DAC.

#### Figure.2. Design PCB drawing and the picture of the PCB

## Experiment

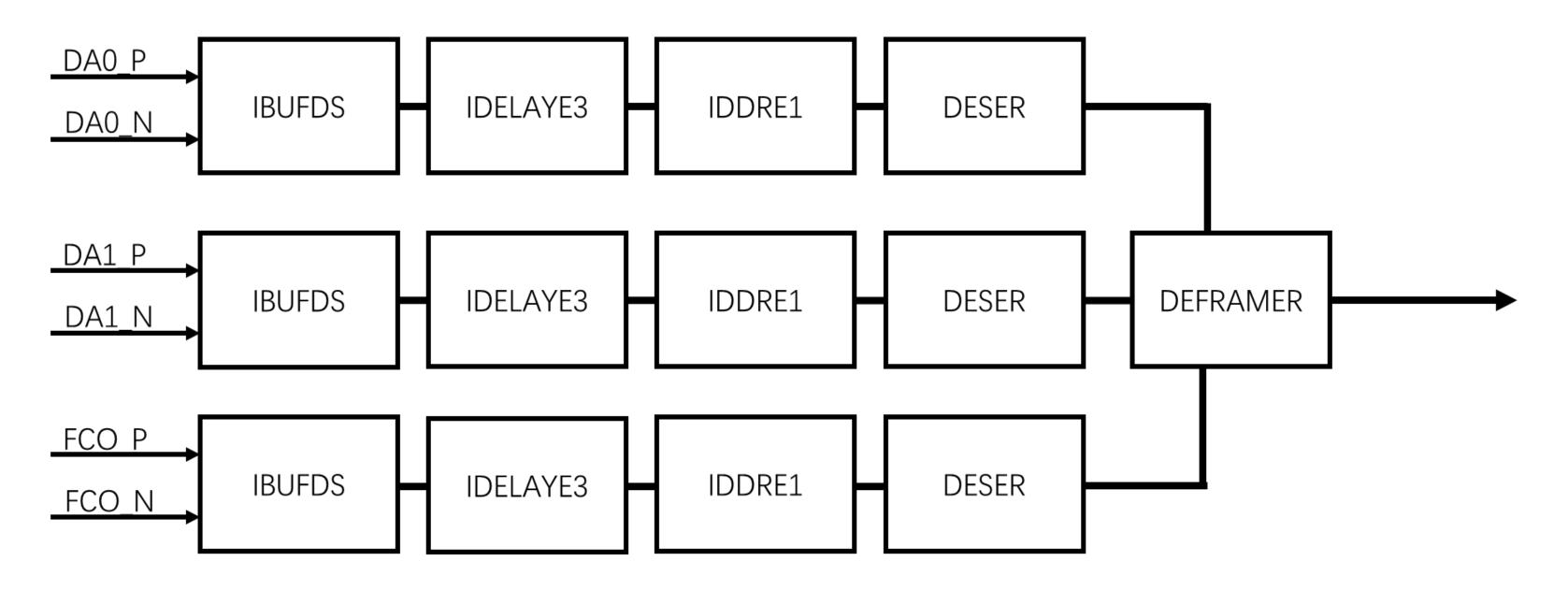

The FPGA readout firmware is designed refer to the timing diagram in the AD9653's datasheet. The ADC readout firmware logic block diagram is shown in Figure 4. The figure shows the readout logic for only one channel; the other channels are similar.

Change the registers of AD9653 through SPI protocol, so that they work in the appropriate state. The FPGA used for data readout is XCKU060-FFVA1156-2. The output of the ADC is read and analyzed by ILA.

Figure.3. AD9653 Readout Logic Block Diagram

### Result

The ADC's ENOB can be as high as 12.6 when using an internal 1.3V reference voltage. The experimental conditions for the figure on the right are an ADC sampling rate of 125 MHz and a sine wave signal source frequency of 10MHz. The following table summarizes the ENOB test results of this design. The ENOB test results of the 8 channels are close, all above 12.6.

#### Table.1. ADC ENOB Experiment Result

| Clock  | Channel | ENOB    |

|--------|---------|---------|

| 125MHz | ch0     | 12.6738 |

| 125MHz | ch1     | 12.6515 |

| 125MHz | ch2     | 12.6382 |

| 125MHz | ch3     | 12.6637 |

| 125MHz | ch4     | 12.6749 |

| 125MHz | ch5     | 12.6536 |

| 125MHz | ch6     | 12.6401 |

| 125MHz | ch7     | 12.6805 |

Qiutong Pan, Department of Engineering Physics, Tsinghua University. Email: panqt22@mails.tsinghua.edu.cn