# The Development of New BPM Signal Processor at SSRF

*†lailw@sari.ac.cn*

Authors: M. J. Zhang, Shanghai University, Shanghai, China also Shanghai Institute of Applied Physics, Chinese Academy of Sciences, Shanghai, China L.W. Lai<sup>†</sup>, Y. M. Zhou, Yingbing Yan, Shanghai Advanced Research Institute, Chinese Academy of Sciences, Shanghai, China H. Jang, S.L.Wang, Nanchang University, Jiangxi, China also Shanghai Advanced Research Institute, Chinese Academy of Sciences, Shanghai, China

•Abstract

**TUP27**

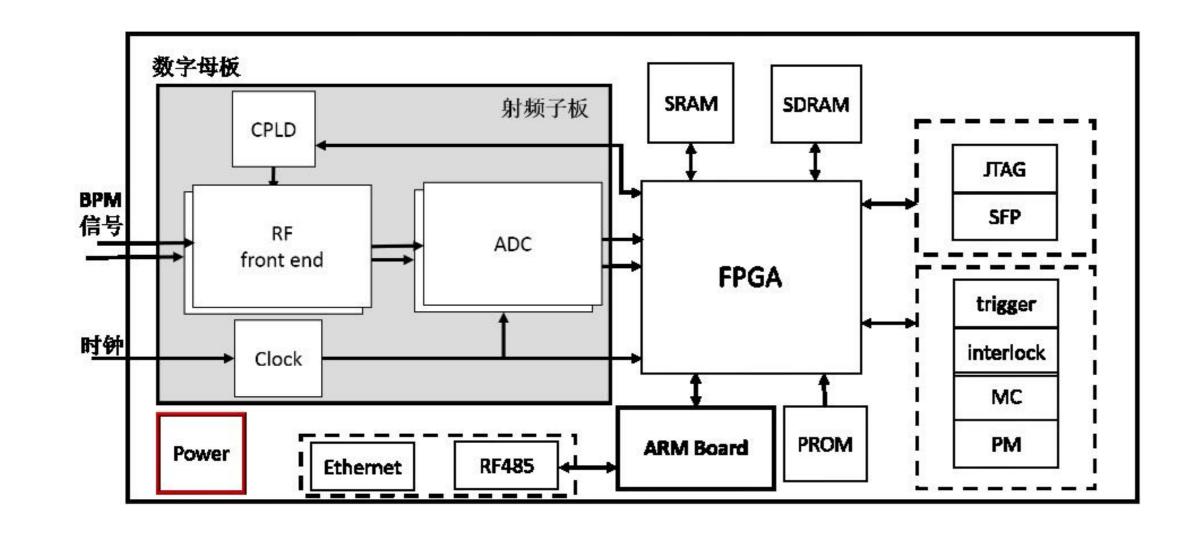

A BPM signal processor has been developed for SSRF since 2009. It composed of Virtex5 FPGA, ARM board, and 4 125MSPS sampling rate ADCs. Since then, electronic technology has made significant progress. Such as Zynq UltraScale+ MPSoC FPGA contains both hard-core ARM and high-performance FPGA, and ADCs with a sampling rate of 1GSPS have been applied in mass production. A new BPM processor with Zynq UltraScale+ MPSoC FPGA and 1GSPS ADCs is under development at SSRF. Due to the application of new technologies, the processor performance will be significantly improved. The new processor can also meet the needs of ultra-low emittance measurement for the new generation of light sources. This paper will introduce the design of the processor and the relative tests.

### •BPM Signal Processor

SSRF developed a new generation of digital backboard with a new generation of system-onchip FPGA (Zynq UltraScale + MPSoC) as the core. It has 8GB PL DDR and more abundant external interfaces, whileupgrading the RF front board, increasing the pilot tone to improve the orbit stability.

| Parameters    | value            |

|---------------|------------------|

| Channels      | 4                |

| ADC bits      | 16               |

| ADC Bandwidth | 650 MHz          |

| Max ADC rate  | 125 MSPS         |

| FPGA          | Xilinx ZCU15EG   |

| Clock         | Ext./Int.        |

| PL DDR4       | 8GB              |

| GPIO          | 12               |

| Trigger       | Ext./Self/Period |

| Interlock     | Lemo             |

| Ethernet      | $2 \times RJ45$  |

| SFP           | 4, UDP&Aurora    |

| Software      | Linux/EPICS      |

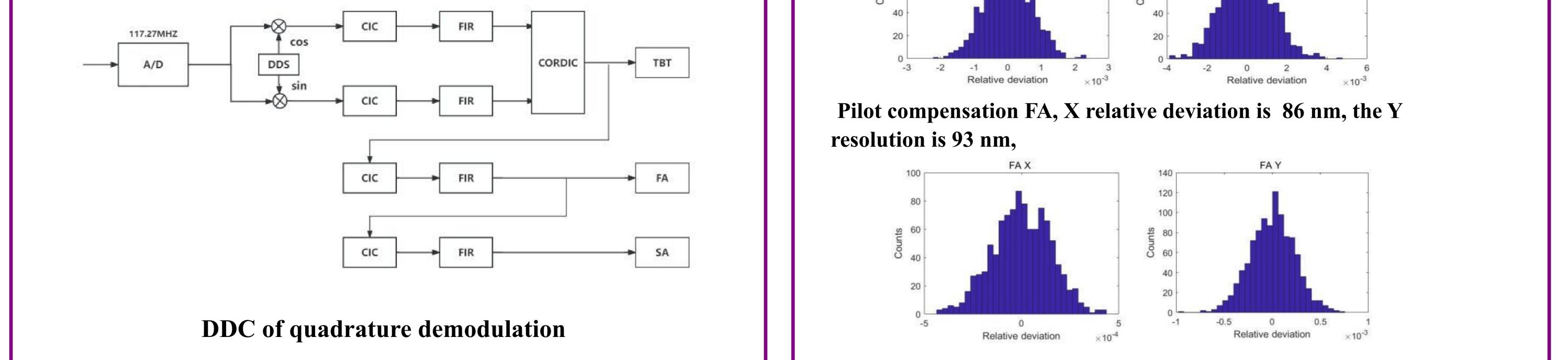

## •BPM digital signal processing

**New RF analog front-end with pilot compensation functions and** integration with the ADC board

**Digital processing backboard**

**RF** analog front-end

### Pilot compensation

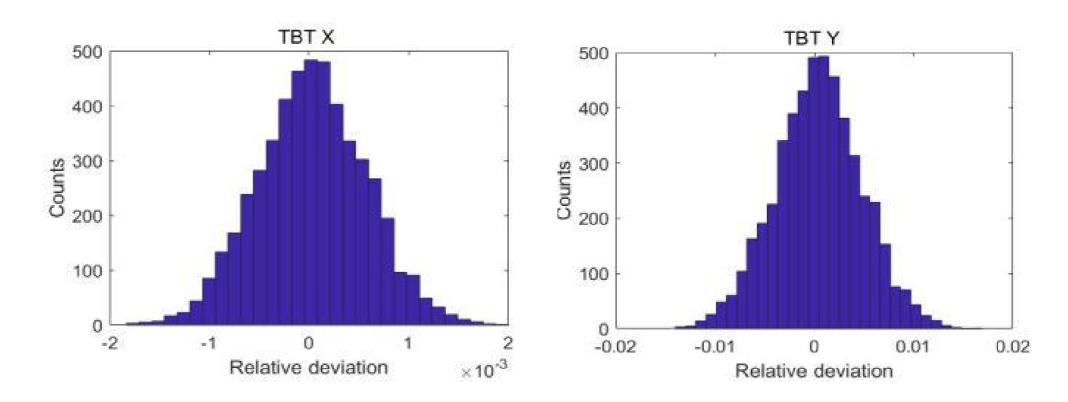

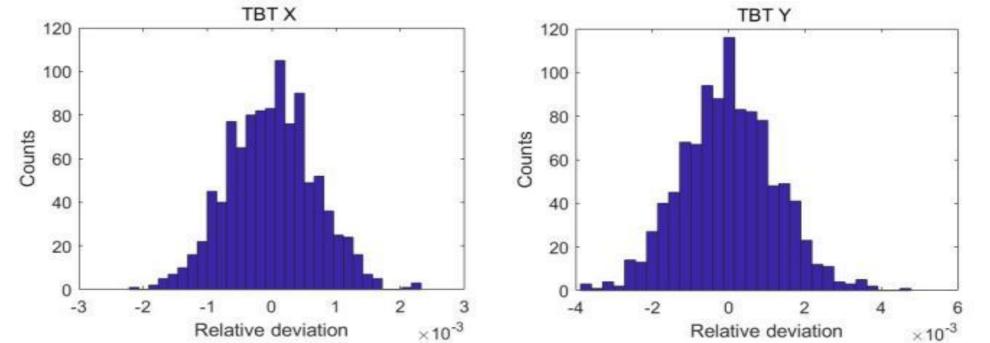

No pilot compensation TBT, X relative deviation is 0.748 µm, the Y resolution is 0.857 μm

Pilot compensation TBT, X relative deviation is 0.392 µm, the Y resolution is 0.496 µm

#### •Conclusion

Based on the pilot compensation scheme, SSRF developed a new BPM digital signal processor prototype with pilot function on the basis of the original self-developed BPM signal processor, and carried out equipment testing and data analysis in the laboratory and storage ring, and obtained that the beam position resolution has been significantly improved.

### **IBIC2024, IHEP, BEIJING, CHINA**